If you want to be an FPGA programmer, which of the two dominant FPGA programming languages do you learn? This question is asked so often by engineers new to the field of digital design, you’d think there would be a definitive answer. In this article I’m going to cover the main differences, pros, and cons about each language.

Before we start, let's review what are the 2 dominant FPGA programming languages?

What is VHDL?

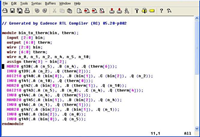

VHDL (VHSIC Hardware Description Language) is a hardware description language used in electronic design automation to describe digital and mixed-signal systems such as field-programmable gate arrays and integrated circuits. VHDL can also be used as a general purpose parallel programming language.

What is Verilog?

Verilog is a hardware description language (HDL) used to model electronic systems. It is most commonly used in the design and verification of digital circuits at the register-transfer level of abstraction. It is also used in the verification of analog circuits and mixed-signal circuits, as well as in the design of genetic circuits.

The Right Question

The wrong question is, “which language should I learn?”. The better question is, “which language should I learn first?”. Surprisingly, it really doesn’t matter which language you learn now, because you’re going to end up working with both. It’s not as scary as it sounds!

Learning Verilog after VHDL (or vice versa) is like getting into shape by running and then switching to cycling after a few months. Either sport will get you into shape, and while the muscle groups you use in the two sports aren’t exactly the same, both activities will make your heart strong enough for either of the sports. Likewise, the concepts you learn in VHDL will transfer easily to Verilog, or the other way around. Don’t get caught up thinking that you’re pinning your FPGA programming career down to one language.

Choose the Language That Suits Your Needs

To answer the question of VHDL vs Verilog, you should really keep in mind your goals and where you’ll be using the language. In the United States, the commercial industries tend to use more Verilog, while the aerospace and defense industries more heavily favor VHDL; the language you learn should reflect which industry you’re more interested in.

Also consider the depth and style you’re comfortable working at. VHDL lends itself to describing hardware at more abstracted levels (like case statements, if/then, etc.), while Verilog is good at describing hardware down to the gate level (nand, xor, etc.). If you’re not familiar with schematic layout or your background is heavy in computer programming, you might be better off using VHDL until you really get familiar with the physical FPGA constructs.

VHDL: A Great Learning Language

If you have no language inclination either way, then my recommendation is VHDL. VHDL is a strongly-typed language, so syntax errors are found more easily by the compiler instead of manually combing through the code looking for an improper usage that is causing problems.

Verilog is somewhat more flexible, but the syntax rules will let you create circuit connections you probably didn’t intend to make, and some of the syntax nuances are confusing for a beginner (wire vs reg). Many engineers who learn Verilog first say that crossing to VHDL was difficult, while I’ve never heard that from the opposite view.

If you have guidance while you learn your first language, like an experienced colleague to help you learn and bounce questions off, then my prefered language is Verilog.

Comparison and Contrast

Beyond considerations for learning your first language, both languages have their advantages and disadvantages.

VHDL

Verilog

If you’re looking to learn either language, there are two “go-to” books for learning hardware description language (HDL). For VHDL, I recommend The Designer’s Guide to VHDL by Peter Ashenden. For Verilog, I recommend Verilog HDL by Samir Palnitkar.

My Message

My Message

Suggestions

Suggestions

Paolo Sanna

2017/2/3 19:55:46

Awesome post. Like it very much.